# PROGRESSIVE AUTOMATED FORMAL VERIFICATION OF MEMORY CONSISTENCY IN PARALLEL PROCESSORS

YATIN AVDHUT MANERKAR

A Dissertation Presented to the Faculty of Princeton University in Candidacy for the Degree of Doctor of Philosophy

Recommended for Acceptance by the Department of Computer Science Adviser: Professor Margaret Martonosi

JANUARY 2021

$\bigodot$  Copyright by Yatin Avdhut Manerkar, 2020.

All rights reserved.

#### Abstract

In recent years, single-threaded hardware performance has stagnated due to transistorlevel limitations stemming from the end of Moore's Law and Dennard scaling. Instead, today's designs improve performance through *heterogeneous parallelism*: the use of multiple distinct processing elements on a chip, many of which are specialised to run specific workloads. The processing elements in such architectures often communicate and synchronise with each other via loads and stores to shared memory. *Memory consistency models* (MCMs) specify the ordering rules for such loads and stores. MCM verification is thus critical to parallel system correctness, but is notoriously hard to conduct and requires examining a vast number of scenarios.

Verification using formal methods can provide strong correctness guarantees based on mathematical proofs, and is an excellent fit for MCM verification. This dissertation makes several contributions to automated formal hardware MCM verification, bringing such techniques much closer to being able to handle real-world architectures. Firstly, my RTLCheck work enables the automatic linkage of formal models of design orderings to RTL processor implementations. This linkage helps push the correctness guarantees of design-time formal verification down to taped-out chips. The linkage doubles as a method for verifying microarchitectural model soundness against RTL. Secondly, my RealityCheck work enables scalable automated formal MCM verification of hardware designs by leveraging their structural modularity. It also facilitates the modular specification of design orderings by the various teams designing a processor. Thirdly, my PipeProof work enables automated all-program hardware MCM verification. A processor must respect its MCM for all possible programs, and PipeProof enables designers to prove such results automatically.

This dissertation also proposes *Progressive Automated Formal Verification*, a novel generic verification flow. Progressive verification emphasises the use of automated formal verification at multiple points in system development—starting at early-stage

design—and the linkage of the various verification methods to each other. Progressive verification has multiple benefits, including the earlier detection of bugs, reduced verification overhead, and reduced development time. The combination of PipeProof, RealityCheck, and RTLCheck enables the progressive verification of MCM properties in parallel processors, and serves as a reference point for the development of future progressive verification flows.

#### Acknowledgements

A dissertation may be the single-authored work of a PhD student, but it is rarely completed due to the efforts of that student alone. In my case, there are many people who have helped me in my journey towards and through grad school, and to whom I offer my sincerest thanks.

First and foremost, I must thank my adviser, Prof. Margaret Martonosi. She gave me an offer of admission when few others did, and has stood by me through both good times and bad. A student's adviser is the most important person in their graduate school travails, and I could not ask for a better adviser than Margaret. I thank her for valuable advice and guidance on a plethora of subjects over the years, and for teaching me how to do research that is truly meaningful. Margaret is an exemplary role model for any young professor to aspire to, and I hope to implement the lessons I learned from her in my future academic career.

I would never have gotten to this point in my life if not for the unconditional love and support of my parents and sister. Whether it was moving to another country with my education in mind, coming to visit me and helping me keep my life in order, giving me a home that was always open to me, or just being a sympathetic ear for the frustrations of grad school, they have *always* been there for me when I needed them. I am eternally grateful for all they have done (and continue to do) for me. I also thank my aunt and her family for being my family in the New York area during my PhD. They were always ready to provide help of a more local nature, and I'm very grateful for all the times that they did.

Dan Lustig has been a valuable mentor and friend to me for my entire time at Princeton. As a senior PhD student, Dan helped me enormously in finding my feet at Princeton and learning how to do research. After he graduated, I benefited from his advice during our weekly teleconferences (which for a while required him to be online at 7:30am). Without him, I may never have looked at memory consistency verification for my PhD research—or gone into formal methods at all. I thank him for showing me that architecture research doesn't have to be about showing 20% speedup on a set of benchmarks, for advice and counsel numerous times over the years, and for being the best damn mentor that any first-year PhD student could ever hope to have. I fondly recall us discussing litmus test  $\mu$ hb graphs on the whiteboard outside our offices in my first year, and I look forward to more such discussions in the future.

Aarti Gupta has been a tremendous positive influence on my dissertation and research trajectory ever since I asked her to serve on my generals committee (on Margaret's advice). I thank her for being my guide to the world of formal verification, for giving me a rigorous foundation of formal methods knowledge on which to build my future research, and for patiently answering all my questions about formal verification, however basic they may have been. Aarti is a veritable ocean of formal verification knowledge. I will never forget the times I asked her what prior work existed on a formal methods topic, and came away with a telling reference that helped me on my way to solving the problem I was facing.

I also thank Margaret, Aarti, Dan, and the other members of my committee, Sharad Malik and Zak Kincaid, for the feedback they have provided on my dissertation work. The questions they raised and the answers I discovered in response have changed this dissertation for the better.

I thank Caroline Trippel—my "research sibling"—for making me laugh, for our many MCM discussions, for teaching me about food and drink, and for valuable job market advice. I must also thank the other current and former members of MRMGroup with whom I interacted over the years: Themis, Tae Jun, Tyler, Aninda, Naorin, Luwa, Prakash, the "Quantum Boyz" Wei and Teague, Marcelo, Yipeng, Esin, Abhishek, Ali, Elba, Logan, Yavuz, Ozlem, and Wenhao. You all are the sauce that makes the meal of grad school palatable, and I am glad to have known each of you. I also thank my other research collaborators, Michael Pellauer and Hongce Zhang, for our productive research discussions.

I'm also indebted to the friends I made at Princeton beyond the confines of our lab. I thank Sumegha Garg and Arjun "Darth" Bhagoji for inviting a lonely grad student to be a part of their friend circles. Through them I made many other friends who I cherish: the Akshays (big and small), Ariel, Nikunj, Divya, Sravya, Gopi, Nivedita, Vivek, Pranav, and Sanjay. I especially thank Arjun and his board game crew for many fun evenings (and for keeping me sane during the pandemic). I thank the PL group—Andrew, Dave, Aarti, Santiago, Qinxiang, Olivier, Joomy, Annie, Ryan, Matt, Nick, Zoe, Lauren, Charlie, Devon, and the rest—for allowing an architect to attend their weekly reading group and for showing me the joys of programming language research. I thank Deep Ghosh for many excellent discussions on *Star Wars* and *The Lord of the Rings*, "Sir" Yogesh Goyal for helpful advice, and both for sharing the joys and sorrows of being a Manchester United fan. And to AB, many thanks for all that you did for me.

I thank the staff at the Davis International Center, especially Katie Sferra, for their assistance in navigating life on a student visa in the US through all the executive orders and presidential proclamations.

I thank Ben Lin for being a stalwart friend through thick and thin for almost 15 years (and hopefully many more), since we were both eager young undergrads at Waterloo. Ben taught me the value of staying positive even in tough times—an essential trait for any grad student.

Finally, while there are many people who helped me through my PhD, there are others who are responsible for me even applying to PhD programs. I thank Tom Wenisch for showing me how much fun research can really be, and for giving me a solid base in computer architecture and parallel computer architecture. I went into my independent work with him looking to get research experience, and emerged with a desire to earn my doctorate. I am very grateful for his support in my decision to come back to academia, and he continues to be someone whose advice I value. I thank Anwar Hasan, Mark Aagaard, and Hiren Patel for awakening my interest in computer architecture at Waterloo. And I thank Mrs. Mitchell, my high school principal, for taking pains to give a young immigrant the best high school education a tiny Canadian town could provide. To my grandfathers, R.M.S.M. and D.D.N.K.,

both great men in their own ways.

# Contents

|   | Abs  | tract . |                                                        | iii |

|---|------|---------|--------------------------------------------------------|-----|

|   | Ack  | nowledg | gements                                                | v   |

| 1 | Intr | oducti  | ion                                                    | 1   |

|   | 1.1  | The R   | ise of Heterogeneous Parallelism                       | 3   |

|   |      | 1.1.1   | The Quest for Improved Hardware Performance            | 3   |

|   |      | 1.1.2   | The Multicore Era and Heterogeneity                    | 4   |

|   | 1.2  | The N   | leed for Memory Consistency Models                     | 7   |

|   | 1.3  | The N   | leed for MCM Verification                              | 12  |

|   | 1.4  | Unreso  | olved Challenges in MCM Verification                   | 16  |

|   | 1.5  | Disser  | tation Contributions                                   | 20  |

|   | 1.6  | Outlin  | le                                                     | 23  |

| 2 | Bac  | kgrou   | nd and Related Work                                    | 25  |

|   | 2.1  | Memo    | ry Consistency Model (MCM) Background                  | 26  |

|   |      | 2.1.1   | Litmus Tests                                           | 26  |

|   |      | 2.1.2   | Speculative Implementations of MCMs                    | 28  |

|   |      | 2.1.3   | Weak/Relaxed MCMs                                      | 32  |

|   |      | 2.1.4   | The Need for Formal MCM Specification and Verification | 38  |

|   | 2.2  | Forma   | l Verification Background                              | 41  |

|   |      | 2.2.1   | Model Checking                                         | 41  |

|   |                                                           | 2.2.2                                                                                     | Interactive Proof Assistants                                    | 48                                                                                                         |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   |                                                           | 2.2.3                                                                                     | Operational and Axiomatic Models                                | 49                                                                                                         |

|   | 2.3                                                       | MCM                                                                                       | Specification and Verification                                  | 50                                                                                                         |

|   |                                                           | 2.3.1                                                                                     | Instruction Set (ISA) Memory Consistency Models                 | 51                                                                                                         |

|   |                                                           | 2.3.2                                                                                     | Program Verification Under MCMs                                 | 53                                                                                                         |

|   |                                                           | 2.3.3                                                                                     | Hardware Ordering Specifications                                | 54                                                                                                         |

|   |                                                           | 2.3.4                                                                                     | Manually Proving MCM Correctness of Hardware Implementations    | 56                                                                                                         |

|   |                                                           | 2.3.5                                                                                     | Dynamic MCM Verification                                        | 57                                                                                                         |

|   | 2.4                                                       | Autom                                                                                     | nated Formal Microarchitectural MCM Verification with PipeCheck | 58                                                                                                         |

|   |                                                           | 2.4.1                                                                                     | Microarchitectural Happens-Before ( $\mu$ hb) Graphs            | 59                                                                                                         |

|   |                                                           | 2.4.2                                                                                     | The $\mu$ spec Domain-Specific Language                         | 62                                                                                                         |

|   |                                                           | 2.4.3                                                                                     | Automatically Verifying Correctness of a Litmus Test            | 64                                                                                                         |

|   |                                                           | 2.4.4                                                                                     | Moving Beyond PipeCheck                                         | 67                                                                                                         |

|   | 2.5                                                       | Summ                                                                                      | ary                                                             | 68                                                                                                         |

|   |                                                           |                                                                                           |                                                                 |                                                                                                            |

| 3 | Che                                                       | ecking                                                                                    | Soundness and Linking to RTL Verification                       | 69                                                                                                         |

| 3 | <b>Che</b><br>3.1                                         | C                                                                                         | Soundness and Linking to RTL Verification                       | <b>69</b><br>70                                                                                            |

| 3 |                                                           | Introd                                                                                    |                                                                 |                                                                                                            |

| 3 | 3.1                                                       | Introd<br>Motiva                                                                          | uction                                                          | 70                                                                                                         |

| 3 | 3.1<br>3.2<br>3.3                                         | Introd<br>Motiva<br>RTLC                                                                  | uction                                                          | 70<br>75                                                                                                   |

| 3 | 3.1<br>3.2<br>3.3                                         | Introd<br>Motiva<br>RTLC                                                                  | uction                                                          | 70<br>75<br>78                                                                                             |

| 3 | 3.1<br>3.2<br>3.3                                         | Introd<br>Motiva<br>RTLC<br>System                                                        | uction                                                          | 70<br>75<br>78<br>80                                                                                       |

| 3 | 3.1<br>3.2<br>3.3                                         | Introd<br>Motiva<br>RTLC<br>System<br>3.4.1                                               | uction                                                          | 70<br>75<br>78<br>80<br>81                                                                                 |

| 3 | 3.1<br>3.2<br>3.3                                         | Introd<br>Motiva<br>RTLC<br>System<br>3.4.1<br>3.4.2                                      | uction                                                          | 70<br>75<br>78<br>80<br>81<br>85                                                                           |

| 3 | 3.1<br>3.2<br>3.3                                         | Introd<br>Motiva<br>RTLC<br>System<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                    | uction                                                          | 70<br>75<br>78<br>80<br>81<br>85<br>86                                                                     |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Introd<br>Motiva<br>RTLC<br>System<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                    | uction                                                          | <ol> <li>70</li> <li>75</li> <li>78</li> <li>80</li> <li>81</li> <li>85</li> <li>86</li> <li>87</li> </ol> |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Introd<br>Motiva<br>RTLC<br>System<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>Handli          | uction                                                          | 70<br>75<br>80<br>81<br>85<br>86<br>87<br>89                                                               |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Introd<br>Motiva<br>RTLC<br>System<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>Handli<br>3.5.1 | uction                                                          | 70<br>75<br>80<br>81<br>85<br>86<br>87<br>89<br>90                                                         |

|   |      | 3.5.4   | Solution: Outcome-Aware Assertion Generation                          | 98  |

|---|------|---------|-----------------------------------------------------------------------|-----|

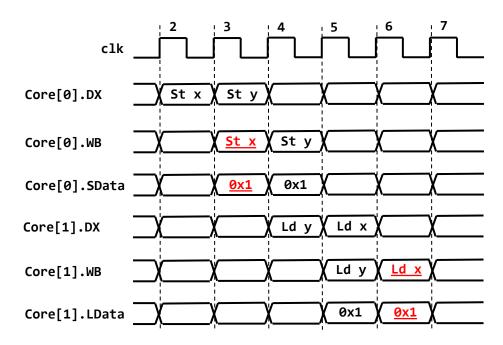

|   | 3.6  | RTLC    | heck Operation                                                        | 100 |

|   |      | 3.6.1   | Assumption Generation                                                 | 101 |

|   |      | 3.6.2   | Overall $\mu$ spec Axiom Translation Procedure $\ldots \ldots \ldots$ | 104 |

|   |      | 3.6.3   | Mapping Individual $\mu$ hb Edges to SVA                              | 105 |

|   |      | 3.6.4   | Mapping Node Existence Checks to SVA                                  | 110 |

|   |      | 3.6.5   | Filtering Match Attempts                                              | 111 |

|   | 3.7  | Case S  | Study: Multi-V-scale                                                  | 112 |

|   |      | 3.7.1   | V-scale Microarchitecture                                             | 113 |

|   |      | 3.7.2   | Multi-V-scale                                                         | 114 |

|   |      | 3.7.3   | Modelling Multi-V-scale in $\mu$ spec                                 | 115 |

|   | 3.8  | RTLC    | heck Methodology and Usage Flows                                      | 115 |

|   |      | 3.8.1   | RTLCheck Methodology                                                  | 116 |

|   |      | 3.8.2   | RTLCheck Usage Flows                                                  | 117 |

|   | 3.9  | Result  | s                                                                     | 117 |

|   |      | 3.9.1   | Bug Discovered in the V-scale Processor                               | 117 |

|   |      | 3.9.2   | RTLCheck Runtimes                                                     | 120 |

|   | 3.10 | Relate  | d Work on Formal RTL Verification                                     | 123 |

|   | 3.11 | Chapt   | er Summary                                                            | 124 |

| 4 | Scal | lable N | ICM Verification Through Modularity                                   | 126 |

|   | 4.1  | Introd  | uction                                                                | 127 |

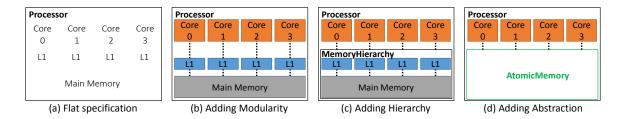

|   | 4.2  | Motiva  | ating Example                                                         | 131 |

|   |      | 4.2.1   | Flat Verification using PipeCheck                                     | 131 |

|   |      | 4.2.2   | Deficiencies of Flat Verification                                     | 133 |

|   | 4.3  | Realit  | yCheck Overview                                                       | 137 |

|   | 4.4  |         | action and its Benefits                                               | 138 |

|   | 4.5  |         | ++ Modular Design Specifications                                      | 140 |

|   |      | , 1     |                                                                       |     |

|   |                          | 4.5.1                                                                                       | Implementation Axiom Files                        | 140                                                                                                                                          |

|---|--------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|   |                          | 4.5.2                                                                                       | Module Definition Files                           | 142                                                                                                                                          |

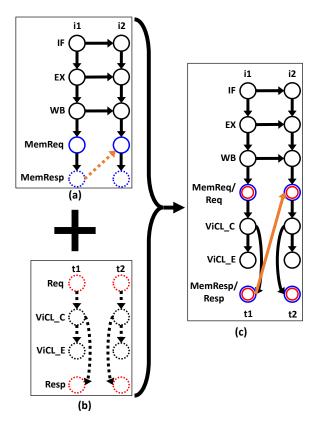

|   |                          | 4.5.3                                                                                       | Interface Specification and Node Mappings         | 148                                                                                                                                          |

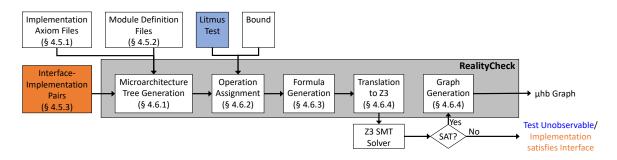

|   | 4.6                      | Realit                                                                                      | yCheck Operation                                  | 148                                                                                                                                          |

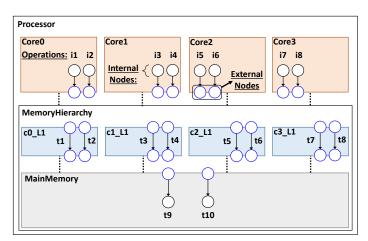

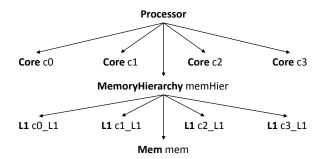

|   |                          | 4.6.1                                                                                       | Step 1: Microarchitecture Tree Generation         | 149                                                                                                                                          |

|   |                          | 4.6.2                                                                                       | Step 2: Operation Assignment                      | 149                                                                                                                                          |

|   |                          | 4.6.3                                                                                       | Step 3: Formula Generation                        | 150                                                                                                                                          |

|   |                          | 4.6.4                                                                                       | Steps 4 & 5: Translate to Z3 and Graph Generation | 151                                                                                                                                          |

|   | 4.7                      | Realit                                                                                      | yCheck Usage Flows                                | 152                                                                                                                                          |

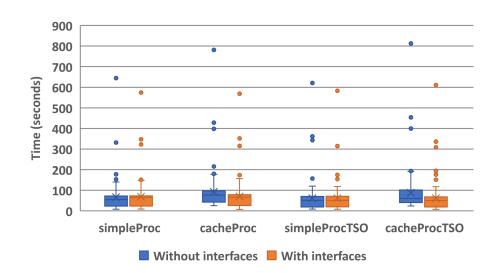

|   | 4.8                      | Metho                                                                                       | dology and Results                                | 154                                                                                                                                          |

|   |                          | 4.8.1                                                                                       | Methodology                                       | 154                                                                                                                                          |

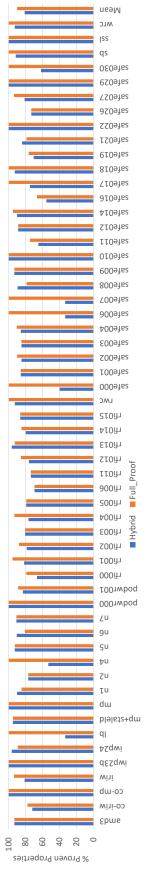

|   |                          | 4.8.2                                                                                       | Verifying Litmus Tests                            | 155                                                                                                                                          |

|   |                          | 4.8.3                                                                                       | Interface Verification                            | 159                                                                                                                                          |

|   |                          | 4.8.4                                                                                       | Bug Finding                                       | 160                                                                                                                                          |

|   |                          |                                                                                             |                                                   |                                                                                                                                              |

|   | 4.9                      | Chapt                                                                                       | er Summary                                        | 161                                                                                                                                          |

| 5 |                          |                                                                                             |                                                   |                                                                                                                                              |

| 5 | Aut                      | omate                                                                                       | d All-Program MCM Verification                    | 163                                                                                                                                          |

| 5 | <b>Aut</b><br>5.1        | omate<br>Introd                                                                             | d All-Program MCM Verification                    | <b>163</b><br>164                                                                                                                            |

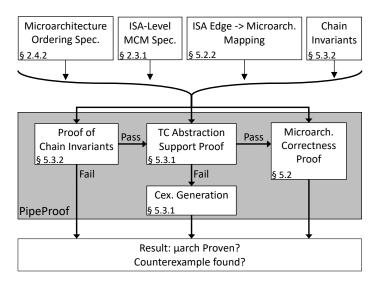

| 5 | Aut                      | omate<br>Introd<br>PipeP                                                                    | d All-Program MCM Verification<br>uction          | <b>163</b><br>164<br>166                                                                                                                     |

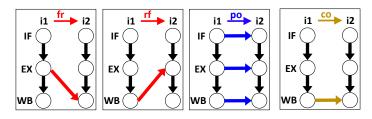

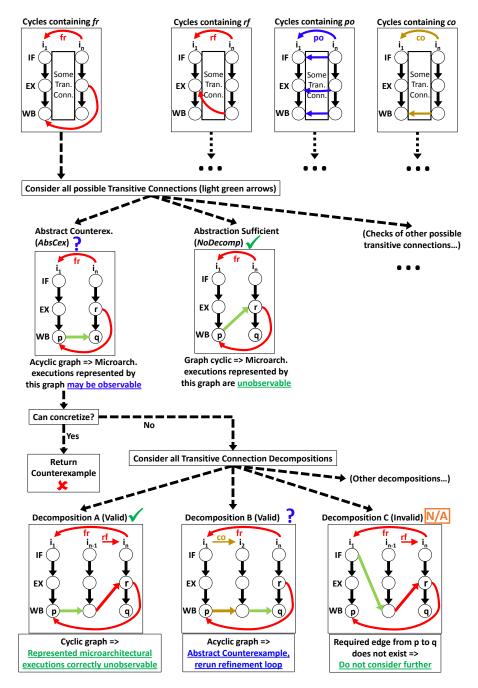

| 5 | <b>Aut</b><br>5.1        | Introd<br>PipeP<br>5.2.1                                                                    | d All-Program MCM Verification<br>uction          | <b>163</b><br>164<br>166<br>169                                                                                                              |

| 5 | <b>Aut</b><br>5.1        | Introd<br>PipeP<br>5.2.1<br>5.2.2                                                           | d All-Program MCM Verification uction             | <ul><li>163</li><li>164</li><li>166</li><li>169</li><li>170</li></ul>                                                                        |

| 5 | <b>Aut</b><br>5.1        | Example 2 Constants<br>Introd<br>PipeP<br>5.2.1<br>5.2.2<br>5.2.3                           | d All-Program MCM Verification uction             | <ul> <li>163</li> <li>164</li> <li>166</li> <li>169</li> <li>170</li> <li>171</li> </ul>                                                     |

| 5 | <b>Aut</b><br>5.1        | Example 2 Constants<br>Introd<br>PipeP<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                  | d All-Program MCM Verification uction             | <ul> <li>163</li> <li>164</li> <li>166</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> </ul>                                        |

| 5 | <b>Aut</b><br>5.1        | introd<br>PipeP<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                | d All-Program MCM Verification uction             | <ul> <li>163</li> <li>164</li> <li>166</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> <li>175</li> </ul>                           |

| 5 | <b>Aut</b><br>5.1        | Example 2 Somate<br>Introd<br>PipeP<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6   | d All-Program MCM Verification<br>uction          | <ul> <li>163</li> <li>164</li> <li>166</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> <li>175</li> <li>176</li> </ul>              |

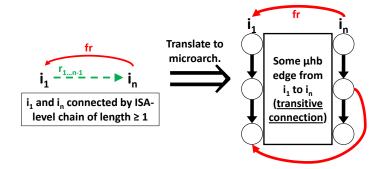

| 5 | <b>Aut</b><br>5.1<br>5.2 | Example 2<br>Introd<br>PipeP<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7 | d All-Program MCM Verification<br>uction          | <ul> <li>163</li> <li>164</li> <li>166</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> <li>175</li> <li>176</li> <li>178</li> </ul> |

| 5 | <b>Aut</b><br>5.1        | Example 2<br>Introd<br>PipeP<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7 | d All-Program MCM Verification<br>uction          | <ul> <li>163</li> <li>164</li> <li>166</li> <li>169</li> <li>170</li> <li>171</li> <li>172</li> <li>175</li> <li>176</li> </ul>              |

|   |                      | 5.3.2   | The Need for Chain Invariants and their Proofs            | 183 |

|---|----------------------|---------|-----------------------------------------------------------|-----|

|   |                      | 5.3.3   | Theory Lemmas                                             | 186 |

|   |                      | 5.3.4   | Over-Approximating to Ensure an Adequate Model            | 186 |

|   |                      | 5.3.5   | Inductive ISA Edge Generation                             | 188 |

|   | 5.4                  | PipeP   | roof Optimizations                                        | 189 |

|   |                      | 5.4.1   | Covering Sets Optimization                                | 189 |

|   |                      | 5.4.2   | Eliminating Redundant Work Using Memoization              | 190 |

|   | 5.5                  | Metho   | odology, Results, and Discussion                          | 191 |

|   | 5.6                  | Relate  | ed Work                                                   | 194 |

|   | 5.7                  | Chapt   | er Summary                                                | 196 |

| 6 | Pro                  | gressiv | ve Automated Formal Verification                          | 197 |

|   | 6.1                  | Testin  | g and Verification in a Traditional Development Flow      | 198 |

|   | 6.2                  | The B   | Cenefits of Early-Stage Design-Time Verification          | 200 |

|   | 6.3                  | The N   | leed for Post-Implementation Verification                 | 203 |

|   | 6.4                  | Verific | eation at Intermediate Points in the Development Timeline | 204 |

|   | 6.5                  | Progre  | essive Automated Formal Verification                      | 206 |

|   | 6.6                  | Chapt   | er Summary                                                | 211 |

| 7 | $\operatorname{Ret}$ | rospec  | tive, Future Directions, and Conclusion                   | 213 |

|   | 7.1                  | Zoomi   | ing Out: The Check Suite for MCM Verification             | 213 |

|   | 7.2                  | Lessor  | ns Learned: A Retrospective                               | 216 |

|   |                      | 7.2.1   | Importance of Operational Model Support                   | 216 |

|   |                      | 7.2.2   | Benefits of a Type System for $\mu$ spec and $\mu$ spec++ | 219 |

|   | 7.3                  | Future  | e Work                                                    | 221 |

|   |                      | 7.3.1   | Furthering Automated All-Program MCM Verification         | 221 |

|   |                      | 7.3.2   | A Unified Modelling Framework Supporting Axiomatic and    |     |

|   |                      |         | Operational Models                                        | 223 |

|   |     | 7.3.3  | Progressive Verification of Other Domains                   | 224 |

|---|-----|--------|-------------------------------------------------------------|-----|

|   |     | 7.3.4  | Developing Abstractions and Concurrency Models for Emerging |     |

|   |     |        | Hardware                                                    | 225 |

|   | 7.4 | Disser | tation Conclusions                                          | 228 |

| A | Har | dware  | Features and Attributes That Impact MCM Behaviour           | 235 |

|   | A.1 | Non-F  | TFO Coalescing Store Buffers                                | 235 |

|   | A.2 | Out-of | f-order Execution                                           | 237 |

|   | A.3 | Depen  | idencies                                                    | 238 |

|   | A.4 | Relaxi | ing Write Atomicity                                         | 240 |

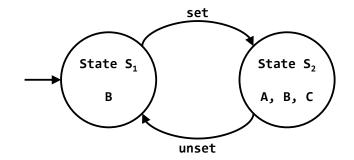

|   | A.5 | Cache  | Coherence and its Relationship to MCMs                      | 243 |

|   | A.6 | Cumu   | lativity                                                    | 245 |

|   | A.7 | Virtua | al Memory                                                   | 246 |

|   | A.8 | Summ   | ary                                                         | 247 |

| - |     |        |                                                             |     |

#### Bibliography

### Chapter 1

## Introduction

"Non omnia possumus omnes, but at least we can step into a boat at a stated time, can we not?" —PATRICK O'BRIAN Post Captain

Computing today has permeated deep into our daily lives. We rely on computers to run our phones, process financial transactions, navigate when travelling, and for many other functions. In other words, computing has become an indispensable tool for humanity to function. This trend will only increase in future years, with the rise of artificial intelligence (AI) and the development of cyber-physical systems like robots and self-driving cars.

The continued importance of computing in our daily lives makes it critical to ensure that these systems run correctly. The ubiquity of computing today means that the ramifications of hardware and software bugs are higher than ever. Computing bugs today can lead to car crashes [Lee19], Internet outages [Str19], and the leakage of confidential information [KHF<sup>+</sup>19].

At the same time, computing systems have evolved over time to become considerably more complex in the quest for improved performance and energy efficiency. Today's microprocessors are complex integrated circuits consisting of a variety of components working together, and are capable of executing billions of instructions per second [Wal18]. Likewise, today's software is also quite complex, consisting of vast numbers of individual modules connected to each other, and often running on large and distributed collections of nodes. Such software may be comprised of millions of lines of code [Alg17]. These factors make verification of today's computing systems a difficult task.

A key contributor to the complexity of systems today is the fact that they are *parallel* systems. Processors today routinely contain at least 4 to 8 general-purpose processing cores that can operate concurrently, and may contain over 40 accelerators for speeding up specific types of computation [WS19]. On the software side, programming languages today routinely have native support for concurrent threads of computation. These threads and cores process data concurrently and often communicate via shared memory. The *memory consistency model* (MCM) of such a system specifies the ordering rules for the memory operations that are used for such communication. Consequently, if parallel systems do not obey their MCMs, then they are liable to malfunction. This makes verification of MCM implementations critical to parallel system correctness.

The work contained in this dissertation makes significant advances towards thorough, comprehensive verification of MCM properties in both parallel hardware. This chapter provides an overview of the challenges in MCM verification and the solutions proposed by this dissertation to meet those challenges. I begin by examining the trends in systems that have led to MCMs becoming a critical part of most computing systems today.

#### 1.1 The Rise of Heterogeneous Parallelism

#### 1.1.1 The Quest for Improved Hardware Performance

For decades, the interface that hardware provides to the programmer has been that of an instruction-level abstraction (ISA), where (from the point of view of the programmer) processors execute instructions one at a time and in program order. Beneath this abstraction, computer architects and VLSI engineers improved hardware performance along two major axes. The first avenue for performance improvement was at the circuit level, and is often characterised using a combination of Moore's Law [Moo06a] and Dennard Scaling [DGY<sup>+</sup>74]. Moore's Law predicted that the number of transistors on an integrated circuit would double every two years<sup>1</sup>, giving computer architects more transistors to use for their chip. Meanwhile, under Dennard scaling, reducing the dimensions of transistors by a factor of S increased their maximum switching speed (i.e. the maximum clock frequency of the processor) by a factor of S, but their power density could be kept constant by correspondingly reducing their supply voltage by a factor of S. Roughly speaking, Dennard scaling enabled engineers to reduce a chip to half its size and twice its speed at every new generation of transistors, while consuming the same amount of power.

The second avenue for the improvement of performance was through the development of improved hardware designs or *microarchitectures* (as opposed to circuits). Over the years, numerous microarchitectural innovations and optimizations have been developed. For instance, pipelining broke up the execution of an instruction into a number of pieces, and allowed a processor to execute parts of multiple different instructions in the same clock cycle. Since the work performed in each cycle was reduced, the design could then be run at a higher clock frequency, improving performance. Another

<sup>&</sup>lt;sup>1</sup>Moore initially predicted a doubling of transistors every year, but a decade later revised his estimate to a doubling of transistors every two years [Moo06b].

example is that of CPU caches, which were developed to improve memory latency and reduce the amount of time processors spend waiting on memory [HP17].

Over the years, computer architects also innovated to improve performance through instruction-level parallelism (ILP) [HP17], or the execution of multiple processor instructions in parallel (as opposed to one at a time). ILP includes pipelining, but also a number of other techniques. These techniques include the execution of instructions out of order (when it would not change the results of the computation), prediction of the results of branch instructions before their inputs were ready, and speculative execution of instructions based on the prediction of their inputs or the results of branch prediction. Another technique closely related to ILP is that of memory-level parallelism (MLP), where multiple memory operations are sent to memory in an overlapping or parallel fashion to reduce the overall number of cycles spent waiting on memory [Gle98]. Notably, each of these schemes took care to ensure that their use did not change the results of the program (which was a single stream of instructions).

#### 1.1.2 The Multicore Era and Heterogeneity

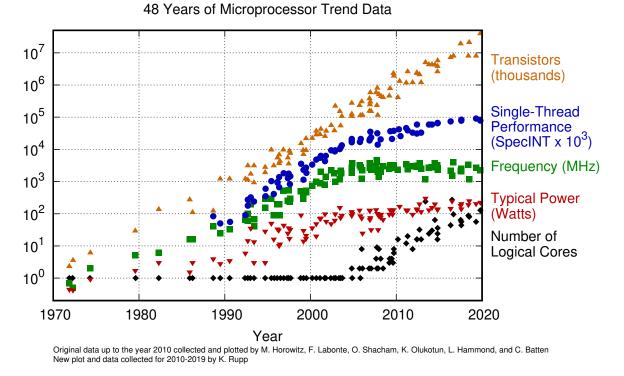

Figure 1.1<sup>2</sup> [Rup20] shows trends in microprocessor data over the last 48 years. It does so by plotting attributes (including processor clock frequency, number of cores, and power usage) of various real processors over that time period. As Figure 1.1 shows, around the mid-2000s, Dennard scaling began to break down, primarily due to leakage power issues. The supply voltage of a transistor ( $V_{DD}$ ) needs to stay above its threshold voltage ( $V_t$ ) in order for the transistor to function as a binary switch. Thus, decreasing  $V_{DD}$  in keeping with Dennard scaling requires decreasing  $V_t$  as well. However, leakage power (power consumed by a transistor regardless of whether it is switching) grows exponentially as threshold voltage decreases [Bos11b]. This makes

<sup>&</sup>lt;sup>2</sup>Figure 1.1 is "48 Years of Microprocessor Trend Data" by Karl Rupp (https://www.karlrupp.net/), and is licensed under the 'Creative Commons Attribution 4.0 International Public License' (https://creativecommons.org/licenses/by/4.0/legalcode).

Figure 1.1: Trends in microprocessor parameters, including clock frequency, power usage, and number of cores over the last 48 years [Rup20].

it impossible to keep power density constant when decreasing transistor dimensions beyond a certain point, leading to the breakdown of Dennard scaling.

While architects and circuit engineers were unable to keep power density constant, they were still able to decrease transistor dimensions and increase the number of transistors on a single chip as per Moore's Law. However, due to the breakdown of Dennard scaling, these devices could not turn all their transistors on at the same time, as the combined power usage of all the transistors would be too high.<sup>3</sup> The issues related to power delivery and dissipation encountered by architects and circuit designers when trying to scale designs beyond the realms of Dennard scaling came to be known as the "power wall" [Bos11b].

Faced with the power wall and the end of Dennard scaling, architects could no longer increase processor clock frequency in order to improve performance. Instead,

$<sup>^{3}</sup>$ In recent years, this inability to activate all transistors at once has become known as the "dark silicon" phenomenon [GSV<sup>+</sup>10].

they began using the extra transistors on chips to create multiple processing *cores*, each of which could execute its own stream of instructions in parallel. Figure 1.1 depicts this through the increase in the number of logical cores per chip from the mid-2000s onwards. Theoretically, an *N*-core version of a processor could provide *N* times the performance of a single-core version of that processor, due to its ability to execute *N* instruction streams in parallel. This would provide large speedups without having to increase clock frequency (and thus power usage). However, the extent to which such a multicore processor can be utilised is dependent on how much the application can be parallelised (i.e., split into multiple pieces that can be run in parallel with each other). For instance, a linear speedup (i.e., *N* times the performance of single-core when using an *N*-core processor) is only possible for applications that can be parallelised into *N* equal parts that can each run in parallel with each other.

In recent years, architects have also begun to adopt *heterogeneity* as a means to develop energy-efficient processors. Heterogeneity is the use of specialised cores for specific types of tasks. Specialising cores to execute specific types of workloads allows architects and circuit engineers to optimise for those workloads, and remove unnecessary general-purpose functionality from such accelerators. This results in huge performance improvements and energy efficiency gains for the workloads that the accelerator is designed for. The field of computer architecture has seen a wide variety of accelerators in recent years, including for machine learning [CDS<sup>+</sup>14] and graph analytics [HWS<sup>+</sup>16] workloads. In fact, the recent Apple A12 System-on-Chip (SoC) contains more than 40 accelerators [WS19].

This heterogeneous parallelism of today's hardware has percolated up the stack to the level of high-level languages (HLLs) and software. Today's programming languages like C [ISO11a], C++ [ISO11b], and Java [GJS<sup>+</sup>14] all have native thread support to enable parallel programming. Operating systems such as the Linux kernel have been revised to be concurrent in order to make the best use of today's parallel

| Thread 0                 | Thread 1                  |

|--------------------------|---------------------------|

| (i1) $x = 1;$            | (i3) $y = 1;$             |

| (i2) if $(y == 0)$ {     | (i4) if $(x == 0)$ {      |

| critical section         | critical section          |

| }                        | }                         |

| Can both threads enter t | their critical section at |

| the same                 | time?                     |

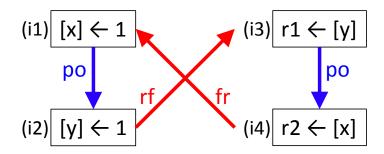

Figure 1.2: A simple synchronisation algorithm based on Dekker's algorithm [Dij02]. This program can be used to illustrate how counterintuitive program outcomes can occur due to MCM issues. The initial values of x and y are assumed to be 0.

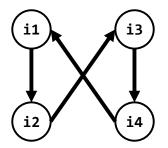

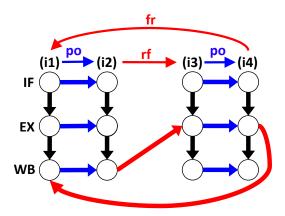

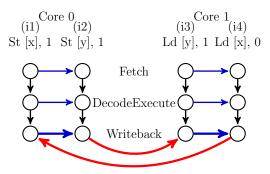

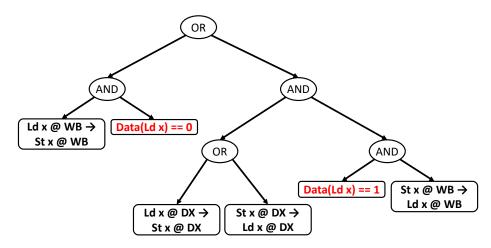

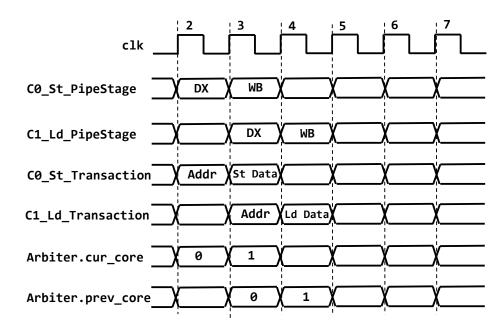

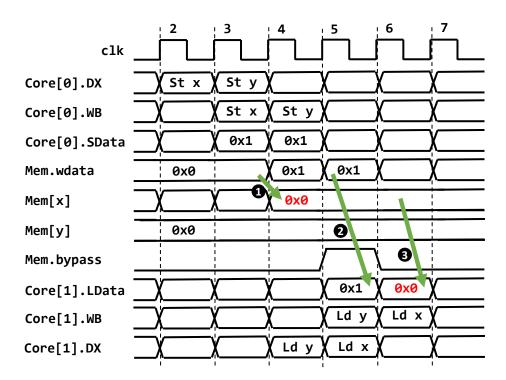

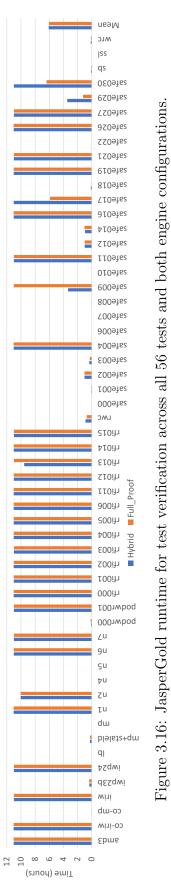

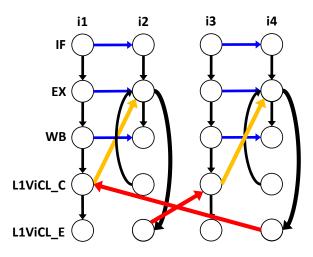

Figure 1.3: The happens-before orderings for Figure 1.2's program that are required for both loads (i2 and i4) to return 0 under SC. The cycle in the graph indicates that such a result is impossible under SC (as it would require an instruction to happen before itself).

hardware [AMM<sup>+</sup>18]. Furthermore, with the advent of heterogeneity, specialised toolchains have been developed for certain types of accelerators. TensorFlow [Goo20] and PyTorch  $[F^+20]$  are two such flows for machine learning accelerators. The programming of systems that support shared-memory concurrency necessitates memory consistency models to describe the behaviour of the parallel system's shared memory, as discussed next.

#### **1.2** The Need for Memory Consistency Models

The various cores in a parallel processor often interact with each other via a shared memory abstraction. Cores thus synchronise and communicate with each other through load and store operations to shared memory. In a single-core system with a single instruction stream, figuring out the result of each load instruction is quite

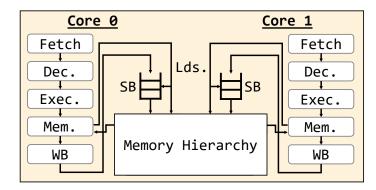

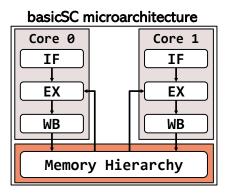

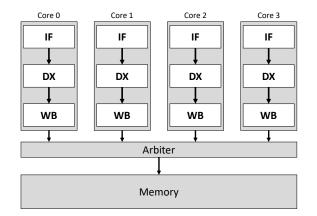

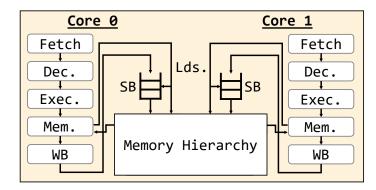

Figure 1.4: A microarchitecture with two cores, each with five-stage pipelines and a store buffer (SB). This design is a simplistic example of how common hardware optimizations like store buffers can lead to weak MCM behaviours.

straightforward. If we define *program order* as the order in which instructions appear in the program's instruction stream, then a load to a given address  $\mathbf{x}$  simply returns the value written by the last store to address  $\mathbf{x}$  before that load in program order. However, in a multicore processor, deducing the values that a load can return is substantially more involved.

Consider the simple synchronisation algorithm in Figure 1.2, based on Dekker's algorithm [Dij02]. Here, two threads each want to access the same shared resource in their critical section. Assume all addresses have a value of 0 before the execution of the program. Each thread has one flag variable (which is shared with the other thread): thread 0's flag is x and thread 1's flag is y. In this synchronisation algorithm, each thread sets its own flag and then reads the value of the other thread's flag. A thread only enters its critical section if its flag is set and the other thread's flag is not set. Can the loads in Figure 1.2's program return values other than 1 or 0? Is it valid for both loads (i2 and i4) to return a value of 0 in the same execution? These questions necessitate a specification for the behaviour of the parallel processor's shared memory abstraction, called a *memory consistency model* or *memory model* [AG96], henceforth abbreviated as MCM.

MCMs specify the ordering rules for memory and synchronization operations in parallel programs. In essence, they dictate what value will be returned when a parallel program does a load. Since the multicore era, the ISA specifications of parallel processors have been updated to include MCM specifications for processors implementing those ISAs. The simplest and most intuitive MCM is *sequential consistency* (SC), defined by Leslie Lamport in 1979 [Lam79]. Under sequential consistency, the results of the overall program must correspond to some in-order interleaving of the program statements or instructions from each individual core or thread. Each core or thread must execute its memory operations in program order. Only one thread or core can execute memory operations at any given time. Furthermore, each memory operation must be performed atomically—in other words, it must become visible to all threads or cores at the same time. Each load must return the value of the last store to its address in the overall total order of memory operations corresponding to its execution.

To illustrate SC, consider the execution of Figure 1.2's program. Under SC, can both the loads i2 and i4 return 0 in the same execution? For i2 to return 0, it must execute before i3. Likewise, for i4 to return 0, it must execute before i1. However, since each thread must execute its memory operations in program order, i1 must execute before i2 and i3 before i4. Each of these orderings is reflected by an arrow in Figure 1.3's graph. Together, they form a cycle, indicating that for both i2 and i4 to return 0, one or more of the program statements must happen before itself, which is impossible. Thus, under SC, it is forbidden for both i2 and i4 to return 0 in the same execution. The synchronisation algorithm will therefore work as expected under SC, and at most one thread will be in its critical section at any time.

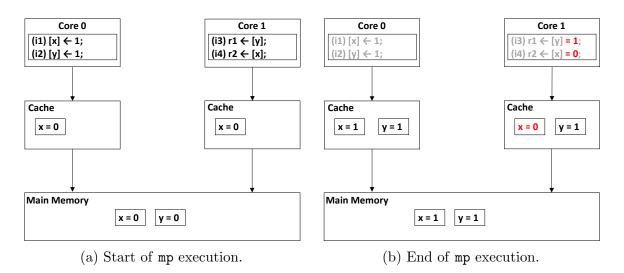

While sequential consistency is a simple and intuitive MCM, its semantics put it at odds with the vast majority of processor microarchitectures today. The microarchitectural optimizations mentioned in Section 1.1.1 were developed in the single-core era, where processors only had one core and one instruction stream operating at any time. Microarchitectural features like store buffers, out-of-order execution, and memory-level parallelism (MLP) routinely reorder the execution of memory instructions to improve performance, but such reordering violates SC. Consider the execution of Figure 1.2's program on the microarchitecture in Figure 1.4, where each core has a five-stage pipeline and its own store buffer [HP17]. (Assume thread 0 runs on core 0 and thread 1 runs on core 1.) Since memory latencies are high, cache misses on stores<sup>4</sup> can notably increase execution time. In this microarchitecture, instead of sending stores directly to the memory hierarchy (and stalling the pipeline until they complete), cores send stores to the store buffer and continue execution of other instructions while waiting for the stores to complete. The store buffer handles sending stores to the memory hierarchy independently of the core's pipeline. The store buffer thus allows the core to overlap the latency of store misses with the execution of other instructions, thus reducing the effective latency of store misses. Subsequent loads check the store buffer for their address to ensure they get the latest value. Loads return the value of the latest entry for their address from the store buffer if one exists, and go to the memory hierarchy otherwise.

While the use of store buffers improves performance, it also makes it possible for both loads (i2 and i4) in Figure 1.2's program to return 0. In particular, store buffers allow core 0 to put i1 in its store buffer and send i2 to memory before i1 has completed, thus reordering i1 and i2 from the point of view of other cores. If we consider thread 0's part of Figure 1.2's program in isolation, then the use of a store buffer would not change the result. The final value of x would be 1, and the final value of y would still be 0. However, in a multicore context, the reordering becomes architecturally visible (i.e., reflected in the values returned by the program's loads). Specifically, core 0 could put i1 in its store buffer, and core 1 could do the same with i3. Then, core 0 and core 1 could send i2 and i4 to memory before the stores i1 and i3 completed, thus allowing both loads to return 0. In a nutshell, the microarchitectural optimizations that were invisible to programmers in a single-core

<sup>&</sup>lt;sup>4</sup>Assuming a write-allocate cache.

setting become programmer-observable when those cores are used in a multicore processor.

In order to implement SC, architects would either have to forgo any optimizations that reordered memory operations or only reorder memory operations speculatively [Hil98, BMW09]. (Section 2.1.2 provides further details on the latter.) Forgoing optimizations that reorder memory operations would result in a huge performance hit, which is unacceptable to the majority of processor users. Meanwhile, speculative reordering of memory operations results in complex designs that must keep track of when reorderings are observed by other cores and roll back appropriately. Furthermore, speculative execution is vulnerable to side-channel attacks [KHF<sup>+</sup>19, TLM18b].

As a result, most of today's processors (including all commercial ones) do not implement SC. Instead, they implement *weak* or *relaxed* MCMs (also known as *weak memory models*) [OSS09, PFD<sup>+</sup>18, AMT14, RIS19] that relax one or more types of orderings among memory operations.<sup>5</sup> For instance, the MCM of x86 processors from Intel and AMD is Total Store Order (TSO) [OSS09], which relaxes orderings between stores and subsequent loads. Thus, unlike SC, TSO allows the outcome of Figure 1.2's program where both loads return 0. To enable synchronization between cores, ISAs that implement weak MCMs provide other instructions capable of enforcing ordering between memory operations where necessary. For example, x86 provides an MFENCE (memory fence) instruction that can be placed between i1 and i2 and between i3 and i4 in Figure 1.2 to prevent the hardware from reordering those two stores. A possible implementation of the MFENCE would be to drain the store buffer before executing any memory operations that are after the MFENCE in program order. (Section 2.1.3 provides further background information on weak MCMs.)

<sup>&</sup>lt;sup>5</sup>Processors implementing weak MCMs may also speculatively reorder memory operations other than those relaxed by their MCM, and roll back such speculation if the speculative reorderings would be detected.

Most programmers do not program in the assembly language of a processor's ISA, but in high-level programming languages like C, C++, and Java. These languages have their own MCMs [ISO11a, ISO11b, GJS<sup>+</sup>14] which describe the behaviour of memory as seen by the various threads in a high-level language program. Most programming language MCMs are based on the SC-for-DRF theorem [AH90, GLL<sup>+</sup>90], which enables the program to behave as if the hardware were implementing SC as long as the programmer has added sufficient synchronization between the threads in their program. Section 2.1.3 contains a brief overview of the SC-for-DRF theorem.

#### 1.3 The Need for MCM Verification

MCMs are defined at interfaces between layers of the hardware-software stack. The MCM of such an interface describes the ordering guarantees that must be provided by lower layers of the stack, and consequently the ordering guarantees that upper layers of the stack can rely on. For example, the MCM of an instruction set like x86 defines the ordering guarantees that must be provided by x86 hardware for any parallel program. Likewise, it defines the ordering guarantees that any x86 assembly-language program can expect the hardware to maintain. Similarly, the MCM of a high-level language like C++ or Java defines the ordering guarantees that a programmer can expect the language runtime to provide for their code. These required orderings must be maintained by the lower layers of the stack—in this case, a combination of the compiler and hardware.

If the layers of a parallel system do not obey their MCMs, then parallel programs will not run correctly on the system. As an example, consider once more the program from Figure 1.2. A programmer might write such code for a processor whose MCM is SC, and use it to synchronise between threads. In such a case, the programmer would expect that at most one thread would be in its critical section at any time (i.e., both loads could never return 0). However, if the processor was buggy and violated SC—for instance, by using store buffers to conduct non-speculative reordering of memory operations—this would no longer be true. It would then be possible for both threads to enter their critical section at the same time, thus breaking the synchronisation mechanism. As such, MCM verification is critical to parallel system correctness.

With concurrent systems becoming both more prevalent and more complex, MCMrelated bugs involving hardware are more common than ever. Intel processors have experienced at least two transactional memory bugs in recent years [Hac14, Int20]. In another case, ambiguity about the ARM ISA-level MCM specification led to a bug where neither hardware nor software was enforcing certain orderings [AMT14, ARM11]. With no cost-effective hardware fix available, ARM had to resort to a low-performance compiler fix instead. MCM-related issues have also surfaced in concurrent GPU programs [ABD+15, SD16]. Finally, the computer security community has recognized that MCM bugs may lend themselves to security exploits [GNBD16]. The work in this dissertation also uncovers an MCM bug in an existing system (see Section 3.9.1). This illustrates that MCM bugs will continue to occur without careful design and the use of verification approaches such as those in this dissertation.

The traditional method of conducting verification is to run tests on the system, but such dynamic verification approaches are insufficient for conducting MCM verification. The reason for this is that today's parallel systems (including multicore processors) are nondeterministic [DLCO09]. This means that a parallel program may give one result when run once on a multicore processor, and a different result when run a second time. For instance, even on a processor implementing SC, Figure 1.2 may give one of 3 results: i2 may return 1 and i4 may return 0, i2 may return 0 while i4 returns 1, or both loads may return 1. Which execution occurs depends on the order in which the stores and loads reach memory from the two cores. Furthermore, even two executions that give the same architectural result may differ microarchitecturally. For example, in one execution a load may read a value from the cache (if it was already present there), and in another execution the load might fetch the same value from main memory. As a result, even if a program such as Figure 1.2 were run a million times on a processor and the outcome where both loads return 0 never showed up, this does not guarantee that the outcome will never occur on the processor.

If using dynamic verification, there is no way to guarantee that one has tested all possible microarchitectural executions for a given program. Instead, MCM properties are best suited to be verified using *formal methods*. In formal verification, a *model* (i.e., a representation) of the hardware or software being verified is specified in some form of mathematical logic. The verification procedure then uses mathematical techniques to formally prove the correctness of the model. Provided that the model accurately represents the system being verified, a proof of the model's correctness implies that the hardware or software is in fact correct. For the rest of this dissertation, unless otherwise specified, I use the term "verification" to mean verification using formal methods. Meanwhile, I use the term "validation" to mean all techniques for checking or ensuring the correctness of a system, including both dynamic testing-based methods and formal verification.

Formal verification approaches can vary in the degree of automation they support. One one end, some formal verification methods (e.g., Kami [VCAD15,CVS<sup>+</sup>17]) require users to manually write proofs of theorems in a proof assistant, and an automated tool then checks that the proofs do indeed prove the corresponding theorems. On the other hand, formal verification approaches like *model checking* [CHV18] (Section 2.2.1) generally only require users to write a specification of the system and the property they wish to verify. An automated tool then either proves the property correct or returns a *counterexample* (an execution that does not satisfy the property). Other verification approaches may be partially automated, e.g., Ivy [PMP<sup>+</sup>16] conducts interactive verification guided by the user. The work in this dissertation utilises automated formal verification approaches based on model checking. Section 2.2 provides further background on formal verification.

Since MCMs are defined for both processor ISAs and high-level programming languages, MCM verification is a full-stack problem.<sup>6</sup> Hardware engineers need to verify that their processor correctly implements its MCM, but writers of compilers for high-level languages must also ensure that the code generated by their compilers maintains the ordering guarantees of the high-level language MCM. If either the hardware or compiler do not maintain their required MCM guarantees, parallel programs will not run correctly on the hardware. Furthermore, if the hardware and software do not agree on who is responsible for maintaining which part of highlevel language MCM guarantees, this can result in incorrect program executions as well [ARM11].

In this dissertation, the term "MCM verification" refers to verification that hardware and the software runtime of a high-level language (e.g. compiler and OS) correctly maintain the MCM guarantees of the hardware ISA and the high-level programming language. In contrast, this dissertation does not focus on program verification under various MCMs [ND13, OD17, AAA<sup>+</sup>15, AAJL16, AAJ<sup>+</sup>19, KLSV17, KRV19], which assumes that the hardware and software runtime correctly maintain MCM guarantees and verifies that a program satisfies its high-level specification (i.e., the programmer's intent). (Section 2.3.2 surveys prior work on program verification under various MCMs.)

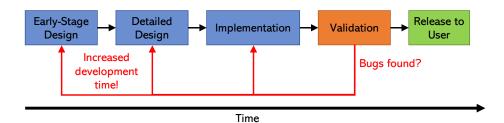

In addition to being a factor across the hardware/software stack, MCMs have ramifications throughout the hardware design timeline. While verification is traditionally thought of as something that is conducted post-implementation, one can derive large benefits by beginning hardware MCM verification much earlier. At the point of early-stage processor design, the choice of MCM for a processor can enable or

<sup>&</sup>lt;sup>6</sup>MCMs are sometimes also defined for intermediate representations, like the LLVM IR [CV17] or NVIDIA PTX [LSG19].

preclude the use of certain microarchitectural features. For instance, choosing SC as a processor's MCM prevents the use of store buffers (except through speculation and rollback; see Section 2.1.2). If a processor design utilises microarchitectural features (or a combination thereof) that violate its MCM, but this design flaw is only caught in post-implementation verification, then this necessitates a redesign (significantly delaying the development of the chip) or a software workaround [ARM11] (which can be heavy-handed and reduce performance). It would be much more efficient to catch such design bugs as early as possible by conducting design-time MCM verification during early-stage design.

As the design evolves, MCM verification should continue to be conducted to ensure that the development of the design does not introduce any bugs that would violate the MCM. Of course, once the design is implemented in Register Transfer Language (RTL) like Verilog, the implementation must also be verified to ensure that it meets MCM requirements.

#### 1.4 Unresolved Challenges in MCM Verification

In response to the need for MCM verification, there has been a large amount of work on formally specifying and verifying MCMs in the past decade or so. (Chapter 2 provides a survey of this related work.) A large portion of prior formal MCM specification and verification work treated hardware as correct (i.e. matching architectural intent) and/or only verified the MCM correctness of hardware using dynamic testing [OSS09,AMSS11, SSA<sup>+</sup>11,MHMS<sup>+</sup>12,AMT14,ABD<sup>+</sup>15,GKM<sup>+</sup>15,FGP<sup>+</sup>16,WBBD15,WBSC17,FSP<sup>+</sup>17, AMM<sup>+</sup>18,CSW18,PFD<sup>+</sup>18]. As Section 1.3 above explains, dynamic testing cannot guarantee the absence of bugs (even for tested programs) due to the nondeterminism of today's multiprocessors. As such, there existed a gap in the MCM verification of parallel systems that needed to be filled through the development of formal MCM verification approaches for hardware designs and implementations.

In recent years, there have been two lines of work for the formal MCM verification of hardware. One approach, Kami [VCAD15,CVS<sup>+</sup>17], enables designers to write their hardware in a proof assistant and manually prove its correctness. A proof assistant like Coq [Coq04] is a tool that aids users in writing proofs of theorems that they can specify in the proof assistant. The proof assistant is capable of verifying whether the user's proof does indeed prove the theorem it purports to, using an approach based on programming language type checking [Chl13]. It also keeps track of what techniques have been used in the proof and what remains to be proven. While Kami is capable of proving the MCM correctness of hardware designs, the proofs require a large amount of manual effort and formal methods expertise. Thus, to produce an efficient formally verified hardware design using Kami, one would need expertise in both computer architecture and formal methods. However, most computer architects do not have formal methods expertise (and vice versa). As such, Kami is not well-suited for use by typical computer architects. (Section 2.3.4 provides further background on Kami.)

The other prior approach for formal MCM verification of hardware designs is PipeCheck [LPM14, LSMB16], which is based on model checking [CHV18]. (Sections 2.2.1 and 2.4 provide further background on model checking and PipeCheck respectively.) PipeCheck was the first automated approach for MCM verification of hardware designs against ISA-level MCM specifications. Given a microarchitectural ordering specification for a hardware design and a litmus test<sup>7</sup> outcome, PipeCheck is capable of automatically verifying whether the given outcome will ever be observable on the design. PipeCheck verifies one test program at a time, and its automation enables it to be used by computer architects rather than just formal methods experts.

$<sup>^{7}\</sup>mathrm{A}$  small 4-8 instruction program used to test or verify MCM implementations. Section 2.1.1 covers litmus tests in detail.

In this dissertation, I use the term "PipeCheck" to refer to the current incarnation of the PipeCheck approach as realised in its follow-on work COATCheck [LSMB16]. COATCheck built on the initial PipeCheck work [LPM14] by adding a domain-specific language ( $\mu$ spec) for specifying microarchitectural orderings and developing a custom SMT solver to conduct PipeCheck's model checking. COATCheck also added the ability to specify and verify microarchitectural orderings related to virtual memory, but this capability is largely orthogonal to the advances made in this dissertation. Section 2.4 provides further details on the PipeCheck approach.

Even with the creation of PipeCheck, there still remained a number of unsolved research challenges in MCM verification. One such challenge is that of verifying model soundness. If a model is sound with respect to a system, then a proof of the model's correctness will imply that the real system is in fact correct. Using an unsound model can result in false negatives (i.e., the model can be formally verified as correct, but the real system is incorrect) which allow bugs to slip through formal verification. Despite the importance of verifying model soundness, prior work either provided no method for soundness verification or only verified model soundness using dynamic testing. For example, if creating a PipeCheck model for the verification of an existing processor, PipeCheck provides no way to formally verify that such a model is sound with respect to the real processor implementation written in RTL like Verilog. Similarly, the formal models of existing ISA-level MCMs (Section 2.3.1) were only verified for soundness against existing implementations of those ISAs through dynamic testing and consultation with architects. In other words, neither ISA-level MCM specifications nor PipeCheck models have been formally verified as being sound with respect to real processor RTL. This increases the possibility of bugs going undetected when such models are used for formal verification.

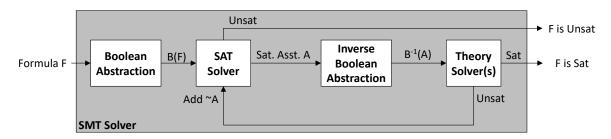

Another unsolved challenge is that of verification *scalability*. The monolithic MCM verification of approaches like PipeCheck does not scale to large detailed designs such

as those used in commercial processors. This is because—like many model checking approaches [BSST09]—PipeCheck uses Satisfiability Modulo Theories (SMT) solvers<sup>8</sup> which are NP-complete [Coo71]. As such, once verification queries are beyond a certain size, the tool's runtime and/or memory usage tends to explode. Approaches like PipeCheck verify the MCM correctness of a design as a single unit, so it is infeasible to use them to verify detailed designs.

A third challenge is that of verification *coverage*. The vast majority of prior automated MCM verification approaches [AMT14, LPM14, LSMB16, WBSC17] only conduct litmus test-based verification or *bounded* verification of a set of test programs.<sup>9</sup> While verifying a processor or compiler for a large number of tests gives engineers confidence that their system is correct, there always remains the possibility that the system contains a bug which can only be detected by a program not present in the test suite. Furthermore, there are an infinite number of possible programs, so they cannot each be tested individually. For hardware MCM verification, engineers had to choose between manual verification across all programs using Kami or automated verification for a bounded set of programs using PipeCheck. No single prior approach provides automated all-program hardware MCM verification.

A fourth challenge deals with the need for MCM verification at multiple points in the development timeline of a system. For example, PipeCheck is intended for MCM verification of early-stage designs, long before they are implemented in RTL. However, MCM verification of RTL implementations is crucial as well, because even if a design is verified as being correct, a buggy implementation of that design in RTL may still violate the processor's MCM. Even so, PipeCheck provides no way to link

<sup>&</sup>lt;sup>8</sup>Given a propositional logic formula F, a Boolean satisfiability (SAT) solver can examine all possible assignments to the variables in F. If an assignment to the variables exists which makes F true, the solver will return that assignment. Otherwise it will return that the formula is *unsatisfiable*. SMT builds on SAT, adding the ability to express properties and systems using various theories, thus improving both expressibility and verification performance. Section 2.2.1 provides further details on SAT and SMT-based model checking.

<sup>&</sup>lt;sup>9</sup>Dodds et al. [DBG18] conduct automated MCM verification of C/C++ compiler optimizations across all possible programs, and their work is a notable exception to this rule.

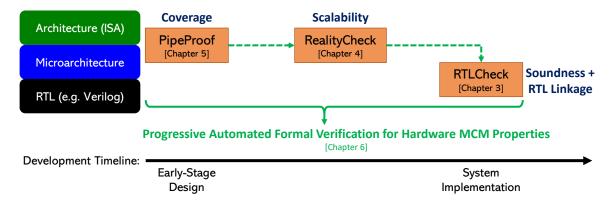

Figure 1.5: The work in this dissertation, organised vertically according to the levels of the hardware/software stack that it covers, and ordered horizontally according to the point in the design timeline it covers. Each work of research is annotated with the challenges in MCM verification that it addresses, as well as the dissertation chapter in which it is covered.

its verification to the verification of the processor's eventual RTL implementations. PipeCheck also provides no easy way for a microarchitectural model to evolve as the design of the processor progresses towards an RTL implementation. There is no straightforward way in PipeCheck to replace the high-level specification of individual components with their detailed design specifications as the design is fleshed out in more detail.

The work in this dissertation develops methodologies and tools to combat these previously unsolved challenges, making large strides forward in the field of MCM verification. These contributions are enumerated next.

#### **1.5** Dissertation Contributions

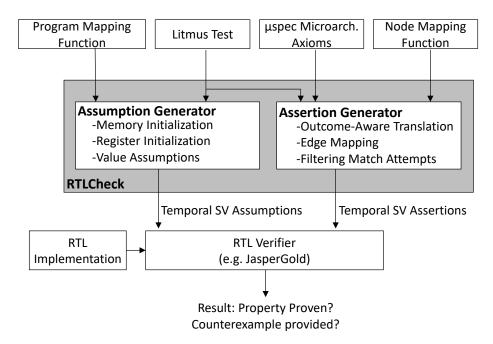

Figure 1.5 provides a graphical depiction of the work in this dissertation. The work is ordered vertically according to the levels of the hardware/software stack that it covers, and is ordered horizontally according to the point in the design timeline it covers. Figure 1.5 also annotates the parts of the dissertation that address the challenges of soundness, scalability, and coverage respectively. This dissertation makes the following contributions:

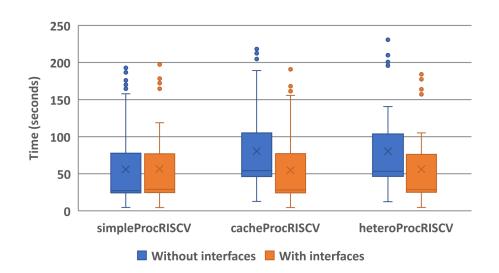

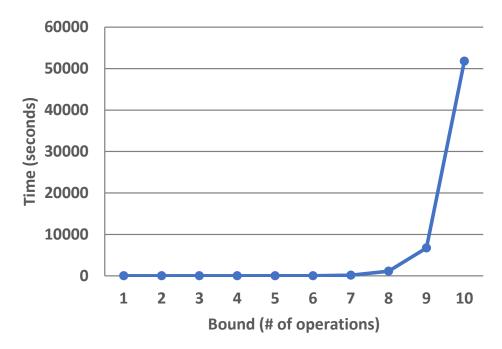

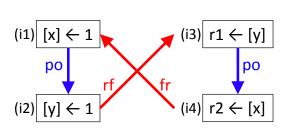

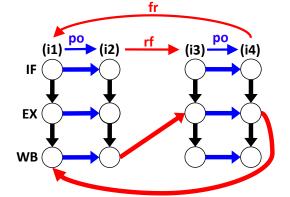

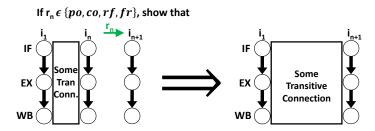

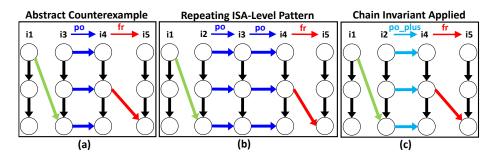

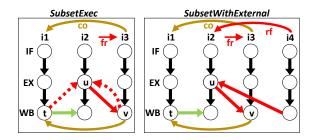

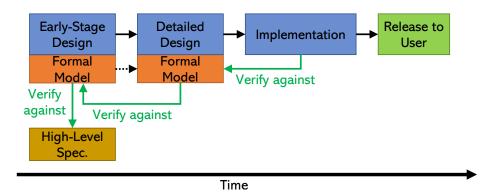

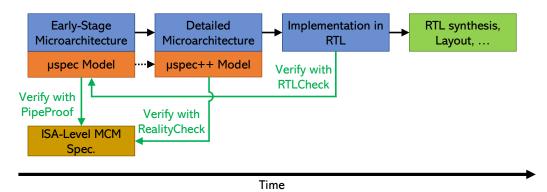

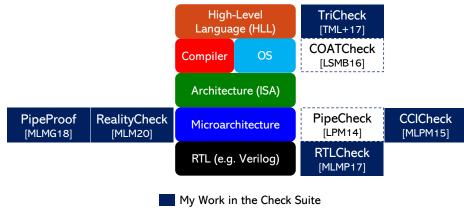

- Linking Automated MCM Verification to Real Processor Implementations: This dissertation enables microarchitectural ordering specifications used for automated MCM verification to be linked to RTL implementations written in Verilog for the first time. Prior work on automated hardware MCM verification only went down to microarchitecture and could not be linked to real implementations, limiting its effectiveness in ensuring the correctness of taped-out chips. The linkage developed by my work (RTLCheck) enables correctness guarantees proven for early-stage design ordering specifications to be easily pushed down to the eventual RTL implementations. The linkage of microarchitectural models to RTL also doubles as a mechanism to formally verify the soundness of a microarchitectural model with respect to RTL. Such soundness verification helps engineers develop accurate formal models of existing processor implementations.